Pcie 4.0 Specification

- Pci_express_base_4.0 Pcie 4.0 Specification 1.0

- Pcie 4.0 Specification Pdf

- Pcie 4.0 Card Electromechanical Specification

- Pcie Pipe 4.0 Specification

PCI Express 4.0 PCI-SIG continues its solid reputation of delivering low cost, high-performance, low-power specifications for multiple applications and markets. O PCI Express 4.0 Specification –(16GT/S). Finalized and published October 2017. Includes new performance enhancements. Maintains position as the interconnect of choice for. The PCI Express 4.0 Timetable Preliminary workshop: Primary purpose is test and specification development. Test results are not required to be shared with device vendors. FYI workshop: Vendors receive pass/fail results but no official integrator’s list. At least 2 FYI workshops are run before official compliance testing begins. PCI Express. (PCIe.) 4.0 capable retimers extend the channel reach on a platform to beyond what is possible otherwise. With PCI Express 4.0 (16 GT/s), data rate has increased by 2x compared to previous generation (8 GT/s), resulting in shorter channel reach.

By Al Yanes, PCI-SIG President and Chairman

I’m pleased to share that PCI-SIG has released the PCIe 4.0 Specification Version 1.0 and it is now available for download on our website. We had previously announced in June this year at our annual DevCon event that the Version 0.9 specification was feature complete and undergoing member IP review. The final published spec describes the PCI Express® architecture, interconnect attributes, fabric management, and the programming interface required to design and build systems and peripherals that are compliant.

The delivery of the PCIe 4.0 specification to the industry is an important addition to our spec library as it delivers high performance 16GT/s data rates with flexible lane width configurations, while continuing to meet the industry’s requirements for low power. Additional functional enhancements include:

- Extended tags and credits for service devices

- Reduced system latency

- Lane margining

- Superior RAS capabilities

- Scalability for added lanes and bandwidth

- Improved I/O virtualization and platform integration

And we’ve seen unprecedented early adoption! Prior to publication, we’ve had numerous vendors confirmed with 16GT/s PHYs in silicon and IP vendors already offering 16GT/s controller. Given the interest, we held a pre-publication Compliance Workshop with preliminary FYI Testing Only for PCIe 4.0 architecture that attracted dozens of solutions. We’re continuing to conduct FYI testing in our workshops throughout the remainder of the year.

PCI-SIG members are welcome to access the PCIe 4.0 spec online at no cost through the PCI-SIG Specification Library. Non-members may purchase the specification here.

PCIe 4.0 is a significant milestone, but we’re not resting. We’ve already released the Version 0.3 of the forthcoming PCIe 5.0 specification, targeted for Q2 2019, which will increase speeds to 32GT/s. For more information on PCI-SIG or PCIe technology, visit our website at www.pcisig.com.

PLDA, the company that designs and sells intellectual property (IP) cores and prototyping tools for ASICs and FPGAs, has optimized its ASIC intellectual property (IP) cores for the next generation of the ubiquitous and general purpose PCI Express® I/O specification, 4.0. PLDA’s proven 3.0 architecture enables easy migration to PCIe 4.0, with no interface changes necessary, and preserves existing behavior for seamless integration.

PLDA has over 20 years of experience in the design of IP cores for ASIC design, specializing in high-speed interface protocols and technologies, with a specific focus on PCIe. Over 6,200 customers have used PLDA cores for several hundred ASIC tapeouts.

PLDA released the first silicon proven PCIe 4.0 Controller IP and the first PCIe 4.0 development platform.

- What is PCIe 4.0?

PCIe 4.0 is the next evolution of the ubiquitous and general purpose PCI Express I/O specification. The interconnect performance bandwidth is double that of the PCIe 3.0 specification achieving 16GT/s and compatibility with software and mechanical interfaces is preserved. PCIe 4.0 architecture is compatible with prior generations of PCIe technology.

Pci_express_base_4.0 Pcie 4.0 Specification 1.0

- Who needs PCIe 4.0?

- Big Data needs throughput

According to Gary King, Weatherhead University Professor, “The data flow so fast that the total accumulation of the past two years—a zettabyte—dwarfs the prior record of human civilization”. Internet, ubiquitous smartphone usage and increased marketing accelerated the Big Data revolution and the Internet of Things (IoT) will increase the needs for fast and efficient data management environments. More Throughput and Lower Power are necessary to prevent a bottleneck in the emergence of Big Data.

- Networking applications

8-lane and 16-lane PCI Express 3.0 have the bandwidth required to handle a 40Gb Ethernet connection. However, using that many lanes raises cost, packaging, and power issues. A higher speed link requiring fewer lanes would be a much better implementation.

- Storage Technologies need more Bandwidth

Data stream provided by PCIe 3.0 (8GT/s) is already sees as a speed limitation for SSD bandwidth. (It can be compared with SAS 12G port that delivers a 12 GT/s data stream). PCIe combined with NVMe will dramatically enhance performance to 16 GT/s per lane.

Pcie 4.0 Specification Pdf

- What is new with PCIe 4.0?

There are no encoding changes from 3.0 to 4.0. There were only minor updates in term of protocol. Indeed, evolution to 4.0 is mostly targeted to address the PHY interface. This is expected to be the most challenging issue for designers to solve.

There are also minor changes in terms of link-level management. PCIe 4.0 enables a more robust equalization.

In term of performance, with PCIe 4.0, throughput per lane is 16 GT/s. The link is full duplex, which means the data can be sent and received simultaneously à Total Bandwidth: 32GT/s. No other industry protocol can achieve the bandwidth of the PCIe 4.0 technology (Up to 64 Gbytes/s of total bandwidth for a PCIe 4.0 x16). New emerging interfaces such as: Ethernet 40G/100G, InfiniBand, solid-state drives (SSDs) and flash memory are demanding bigger pipes. These figues make PCIe architecture the only technology solution that achieves this level of performance with minimal new software upgrades.

- Why choose PLDA's PCIe 4.0 IP ?

- For the reliability:

- For the Flexibility:

Flexibility of the supported PIPE Configurations for PCIe 4.0:

Flexibility of the core configuration to meet spec evolutions

- For the supported features:

Features already proven in 3.0, optimized for the targeted markets of PCIe 4.0

- Endpoint, root port, switch, dual-mode shared silicon

- Virtualization-ready with SRIOV and ATS/ARI (networking, datacenter)

- Multi-function

- AER and data integrity mechanism

- Complete power management support: legacy, ASPM L0s/L1, OBFF, L1 PM substate with CLKREQ

- End-end TLP prefixes

- Because it is optimized for PCIe 4.0 challenges

Extension Devices:

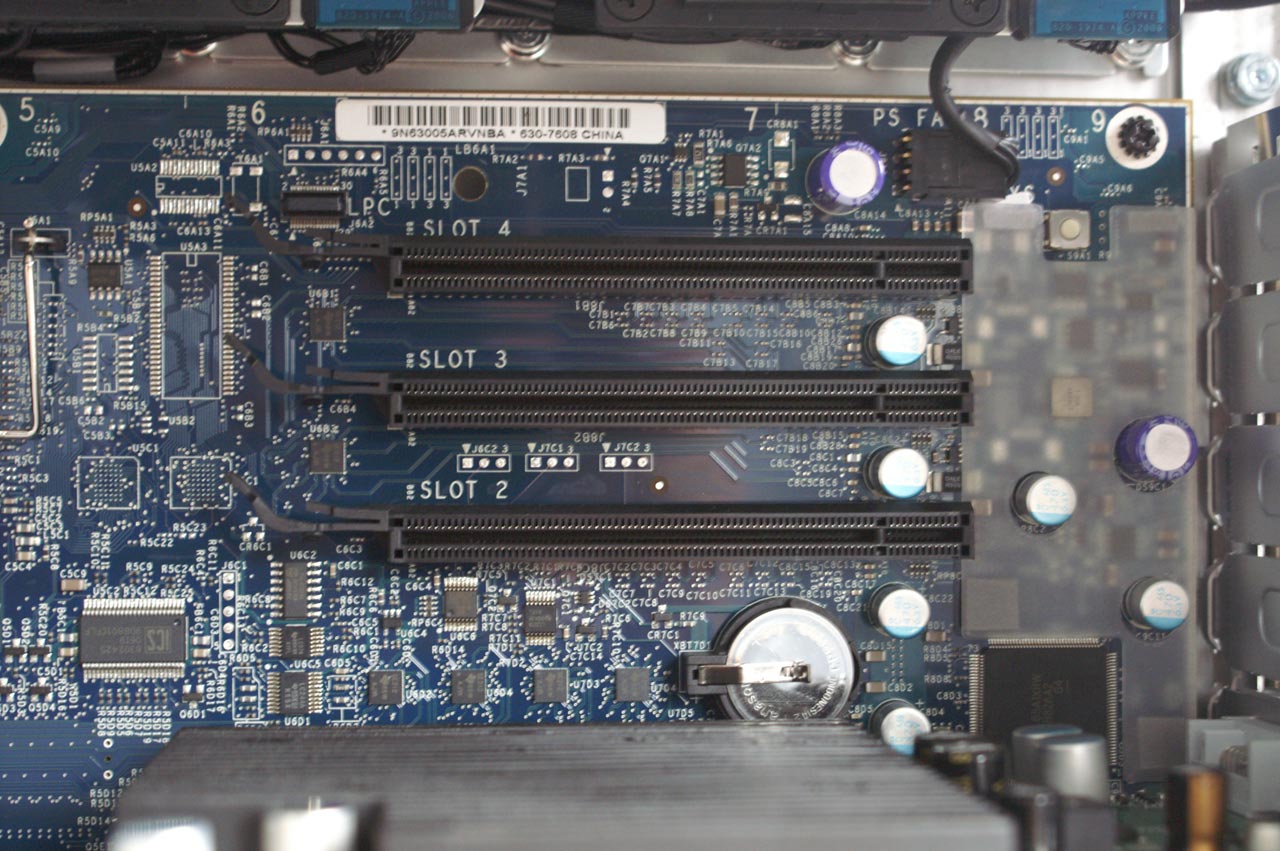

- Re-timer devices are expected to become widespread in PCIe 4.0 motherboards and backlanes.

PLDA IP Core supports Extension Device ECN

Multiple Packets Per Clock Cycle:

- Normal: Received packets are stored in a receive buffer and the user application can extract them one at a time, at its own pace

- RXstream: Received packets are output to the application one at a time providing greater control over ordering and processing.

Pcie 4.0 Card Electromechanical Specification

- For the Multi PHY Compliance:

Pcie Pipe 4.0 Specification

PLDA’s goal is to provide fully integrated “Controller + PHY” solutions for PCIe 4.0 to our customers, targeting various foundry/process combinations. PLDA’s PHY Interoperability test suite for PCIe 4.0 is available to customers and partners (PHY vendors and ASIC vendors). PLDA is partnering with major PHY vendors to have an integrated PHY/Controller solution.